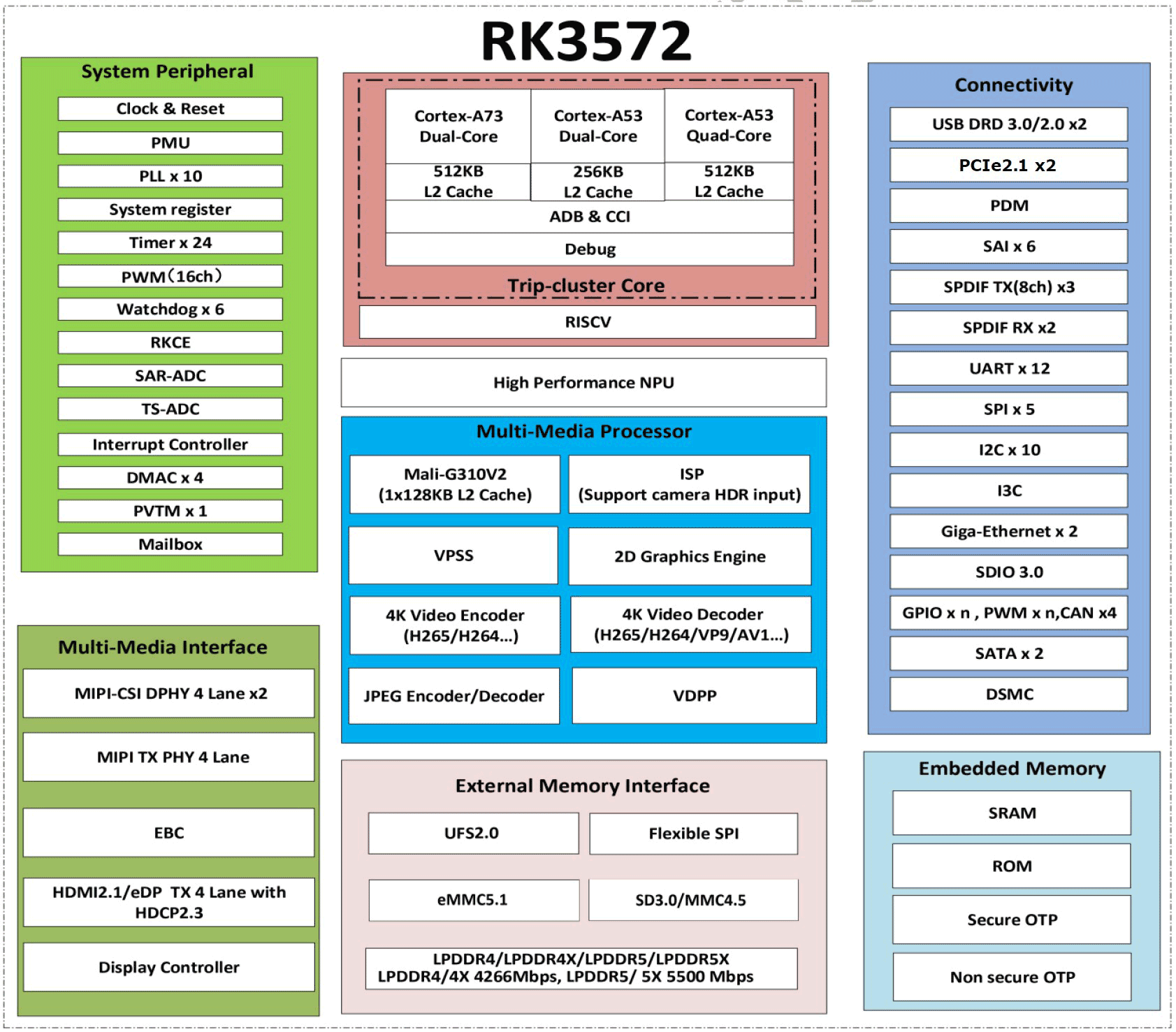

RK3572 is a low power, high performance processor for edge computing device, personal mobile internet device and other AIoT applications, and integrates dual-core Cortex-A73 and hexa-core Cortex-A53 with separately NEON coprocessor.

RK3572 video decoder supports H.265, VP9, AV1 and AVS2 etc., up to 8K@30fps or 4K@120fps, and supports H.264 up to 4K@60fps. Video encoder supports H.264 and H.265 up to 4K@40fps, and high-quality JPEG encoder/decoder supports up to 4K@60fps.

Embedded 3D GPU makes RK3572 completely compatible with OpenGL ES 1.1, 2.0, and 3.2, OpenCL up to 3.0 and Vulkan 1.2. Dedicated 2D hardware engine with MMU will maximize display performance and provide very smoothly operation.

RK3572 introduces a new generation 12-Megapixel ISP (Image Signal Processor). It implements a lot of algorithm accelerators, such as HDR, 3A, CAC, 3DNR, 2DNR, Sharpening, Dehaze, Enhance, Debayer, Small Angle Lens-Distortion Correction and so on.

The built-in NPU supports INT4/INT8/INT16/FP4/FP8/FP16/BF16 hybrid operations, supports for asymmetric MAC operations with W4A16. In addition, with its strong compatibility, network models based on a series of frameworks such as TensorFlow/MXNet/Pytorch/Caffe can be easily converted.

RK3572 supports high-performance external memory interface (LPDDR4/LPDDR4X/LPDDR5/LPDDR5X) capable of sustaining demanding memory bandwidths, and also provides a complete set of peripheral interface to support very flexible applications.

Microprocessor

Microprocessor

-

Cortex A73 cluster

-

Dual Cortex A73 MPCore processor

-

64kB L1 instruction cache and 32kB L1 data cache for each core

-

512kB unified L2 cache

-

-

Cortex A53 cluster 0

-

Quad Cortex A53 MPCore processor

-

32kB L1 instruction cache and 32kB L1 data cache for each core

-

512kB unified L2 cache

-

-

Cortex A53 cluster 1

-

Dual Cortex A53 MPCore processor

-

32kB L1 instruction cache and 32kB L1 data cache for each core

-

256kB unified L2 cache

-

-

TrustZone technology

-

ARMv8 Cryptography Extensions

-

Full implementation of the ARM architecture v8-A instruction set, ARM Neon Advanced SIMD (single instruction, multiple data) support for accelerating media and signal processing

-

Two isolated voltage domains to support DVFS, one is for A73 cluster and the other is for A53 clusters.

-

Independent power domain for each CPU core system (CPU+Neon+FPU+L1 cache).

Memory Organization

-

Internal on-chip memory

-

BootRom

-

Supports system boot from the following devices:

-

FSPI interface

-

eMMC interface

-

UFS interface

-

SD card interface

-

-

Supports system code download by the following interface: USB DRD interface

-

-

PMU_SRAM (16kB) is for low power application

-

SYS_SRAM (512kB) may be shared by any on-chip components

-

-

External off-chip memory

-

Dynamic Memory interface

-

JEDEC standards LPDDR4/LPDDR4X-4266 and LPDDR5/LPDDR5X-5500.

-

Single channel has 32bits data width.

-

Up to 4 ranks (chip select) for each channel.

-

Up to 16GB addressing space totally.

-

Low power mode including power-down and self-refresh with power-down.

-

-

eMMC interface

-

Compliance to JEDEC eMMC v5.1 specification

-

Compatible to eMMC 4.51 and earlier versions specification.

-

Supports HS400, HS200, DDR50 and legacy operating modes

-

Supports data bus width: 4-bit or 8-bit

-

-

SD/MMC interface

-

Compliance to SD v3.0, MMC v4.51

-

-

System Component

-

BUS

-

RISC-V MCU

-

One Nuclei N320 processor core

-

Supports 24kB ILM which can be accessed by instruction and data access

-

8kB I-Cache and 8kB D-Cache

-

JTAG interface for debug

-

-

CRU (clock & reset unit)

-

Supports 10 PLLs to generate all clocks totally

-

Supports one 24MHz oscillator as input

-

Supports clock gating control for individual components

-

Supports global soft-reset control for whole chip, also individual soft-reset for each component

-

-

PMU (power management unit)

-

Supports multiple configurable work modes to save power consumption with different frequency or automatic clock gating control or power domain control

-

Supports many wakeup sources in different working state

-

Supports 7 separate voltage domains

-

Supports 23 separate power domains, which can be power up/down by software based on different application scenes

-

-

Timer

-

Supports 6 secure timers with 64bits counter and interrupt-based operation

-

Supports 18 non-secure timers with 64bits counter and interrupt-based operation

-

Supports 1 high-performance timer

-

Supports two operation modes: free-running and user-defined count for each timer

-

-

PWM

-

Supports 16 on-chip PWMs (PWM0_CH0~PWM0_CH1, PWM1_CH0~PWM1_CH5, PWM2_CH0~PWM2_CH7) with interrupt-based operation

-

Supports input capture mode

-

PWM0 support IR power key capture mode

-

Supports continuous mode and one-shot output mode

-

PWM1 supports generators waveform through lookup table

-

PWM2 supports IR transmission in NEC with full repeat, NEC with simple repeat, TC9012 or SONY mode

-

PWM1 supports clock frequency meter

-

PWM1 supports clock counter

-

PWM1 and PWM2 support biphasic counter

-

Supports two-stage frequency division of working clock

-

-

Watchdog

-

Supports 5 non-secure watchdog and 1 secure watchdog

-

32-bit watchdog counter

-

Counter counts down from a preset value to 0 to indicate the occurrence of a timeout

-

WDT can perform two types of operations when timeout occurs:

-

Generate a system reset

-

First generate an interrupt and if this is not cleared by the service routine by the time a second timeout occurs then generate a system reset

-

-

-

Interrupt Controller

-

Supports 4 PPI interrupt source and 448 SPI interrupt sources input from different components inside SoC

-

Supports 16 software-generated interrupts

-

Input interrupt level is fixed, high-level sensitive for SPI and low-level sensitive for PPI

-

Supports different interrupt priority for each interrupt source, and they are always software-programmable

-

-

DMAC

-

Supports 4 DMA controllers for peripheral system

-

Supports Linked list DMA mode to complete scatter-gather transfer

-

Supports data transfer types including memory-to-memory, memory-to-peripherals and peripherals-to-memory

-

Each DMAC features:

-

Supports 64 logic channels

-

Supports 2 physical channels

-

Supports 64 hardware request from peripherals

-

-

-

Secure System

-

Supports one cipher engine system feature

-

Support 3 AHB slave interfaces KLCE (CE for key-ladder), SCE (CE for secure world) and NsCE (CE for non-secure world) each

-

Support DMA controller to transfer data between CE (Crypto Engine) and memory

-

Supports task descriptor (TD) chain mode for each world request. TD or TD chain are executed at request order

-

Symmetrical algorithms

-

Support lockstep error monitoring

-

Support anti side channel attack

-

Support AES, DES, 3DES, SM4

-

Support AES-128, AES-192, AES-256

-

Support ECB/CBC/OFB/CFB/CTR/CTS/XTS/CCM/GCM/CBC-MAC/CMAC mode for AES and SM4

-

Support ECB/CBC/OFB/CFB mode for DES/TDES

-

-

Hash algorithm

-

Supports lockstep error monitoring

-

Supports SHA-1, SHA-256, SHA-224, SHA-512, SHA-384, SHA-512/256, SHA-512/224, MD5, SM3 with hardware padding

-

Supports HMAC of SHA-1, SHA-256, SHA-512, MD5, SM3 with hardware padding

-

-

Asymmetrical algorithms

-

Support RSA, ECC, SM2

-

RSA512/1024/2048/3072/4096-bit

-

ECC192/224/256-bit

-

-

Support key-ladder (KL)

-

Supports obtaining the root key from OTP or RKRNG

-

Supports writing out root key or the key which calculated by key-ladder to some specific modules by using APB master

-

Number of stages can be configured

-

Supports AES-128, AES-192, AES-256, DES, TDES, SM4

-

Supports ECB/CBC/OFB/CFB mode

-

-

Supports data scrambling for all DDR types

-

Supports secure OTP

-

Supports secure debug

-

Supports secure DFT test

-

Supports secure OS

-

Except CPU, the other masters in the SoC can also support security and non-security mode by software-programmable

-

Some slave components in SoC can only be addressed by security master and the other slave components can be addressed by security master or non-security master by software-programmable

-

System SRAM can be divided into 4 parts; each part can be software-programmable to be enabled by each master

-

External DDR space can be divided into 16 parts; each part can be software-programmable to be enabled by each master

-

-

Mailbox

-

Supports one Mailbox with 14 channels in SoC to provide communication service between CPU and MCU

-

Supports independent interrupt in each Mailbox channel

-

Video Codec

-

Video Decoder

-

Supports video decoder of H.264, H.265, VP9, AV1 and AVS2

-

Supports MMU

-

Supports multi-stream decoding in parallel

-

Decoder table:

-

| Decoder | Profile | Level | Resolution |

|---|---|---|---|

| H.264/AVC | Main | 5.2 | up to 4K@60fps |

| H.265/HEVC | Main | 6.0 | up to 8K@30fps or 4K@120fps |

| VP9 | Profile 0/2 | 6.0 | up to 8K@30fps or 4K@120fps |

| AVS2 | Profile 0/2 | 8.2.120 | up to 8K@30fps or 4K@120fps |

| AV1 | Main | 6.0 | up to 8K@30fps or 4K@120fps |

-

H264 MVC is up to 4K@60fps

-

Video Encoder

-

Supports multi-stream encoding

-

Encoder table:

-

| Encoder | Profile | Level | Resolution |

|---|---|---|---|

| H.264/AVC | High | 5.0 | up to 4K@40fps |

| H.265/HEVC | Main | 5.0 | up to 4K@40fps |

-

JPEG Encoder

-

Supports Baseline (DCT sequential)

-

Supports image size is from 16×16 to 65520×65520

-

Supports MJPG up to 4K@60fps

-

Supports YUV400/YUV420/YUV422/YUV444

-

-

JPEG Decoder

-

Supports image size is from 48×48 to 65520×65520

-

Supports MJPG up to 4K@60fps

-

Supports YUV400/YUV411/YUV420/YUV422/YUV440/YUV444

-

Neural Process Unit

-

Rockchip NPU engine:

-

4 TOPS(1) for INT8

-

Supports INT4, INT8, INT16, FP4, FP8, FP16 and BF16 operation

-

Supports for asymmetric MAC operations with W4A16

-

Supports deep learning frameworks: TensorFlow, Caffe, Tflite, Pytorch, Onnx NN, Android NN, MXNet etc.

-

-

Note (1): Sparsity

Graphics Engine

-

3D Graphics Engine

-

ARM Mali G310V2 MC1 GPU

-

OpenGL ES 1.1, 2.0 and 3.2

-

Vulkan 1.2

-

OpenCL 3.0 Full Profile

-

AFBC (ARM Frame Buffer Compression)

-

-

2D Graphics Engine (RGA)

-

Rockchip RGA v2.5 engine

-

Max resolution: 8192×8192 source, 4096×4096 destination

-

Block transfer and Transparency mode

-

Color fill with gradient fill, and pattern fill

-

Alpha blending including global alpha, per pixel alpha and fading

-

Arbitrary non-integer scaling ratio from 1/16 to 16

-

0,90,180,270-degree rotation, x-mirror, y-mirror & rotation operation

-

RKCFA (Color Filter Array) V1.0 for E-ink screen

-

-

VDPP (Video & Display Post Process)

-

Deinterlace

-

Input data format: YUV420/YUV422 P/SP

-

Output data format: YUV420/YUV422 SP

-

Supports algorithms including 1502, 1501T, 1501B, 1202, 1101T, 1101B and so on

-

Resolution is up to 1920×1080

-

-

Post Process

-

Input data format: YUV420SP

-

Output data format: YUV420/YUV444 SP

-

DMSR: De-Mosquito noise, De-Ringing effect and De-Shooting effect

-

ZME: Zoom Manage Engine (Video resize based Multi-Phase Algorithm)

-

DCI-HIST: Histogram of Dynamic Contrast improvement

-

SHARP: Sharpness

-

ES: Edge Smoothing

-

PYRAMID: Down sample to 1/4,1/16,1/64 resolution

-

-

Video Input Interface

-

Support 2 MIPI CSI-2 interfaces

-

Two 4 data lanes of D-PHY v1.2

-

Each interface may be configured as 2×2 data lanes port.

-

Each port supports 4 virtual channels

-

DVP interface

-

8/10/12/16-bit, up to 150MHz I/O frequency

-

BT.601/BT.656 and BT.1120 VI interface

-

Supports the polarity of pixel_clk, hsync, vsync configurable

-

Supports 2/4 mux byte interleave format for BT.656/BT.1120

-

Supports dual-edge sampling for BT.656/BT.1120

-

Image Signal Processor

-

Video Capture (VICAP)

-

Support BT.601 RAW8/10/12 YCbCr 422 8-bit input

-

Support BT.656 YCbCr 422 8-bit progressive/interlaced input

-

Support BT.1120 YCbCr 422 16-bit progressive/interlaced input

-

Support 2/4 mixed BT.656/BT.1120 YCbCr 422 input

-

Support dual-edge sampling for BT.656/BT.1120

-

Support receiving four groups of MIPI CSI interfaces, up to four IDs for each group

-

Support VC/DT configurable for each ID

-

Support ten MIPI CSI data formats: RAW8/10/12/14/16, RGB888, YUV422 8bit, YUV422 8bit interlaced, YUV420 8bit, Legacy YUV420 8bit

-

Support three modes of MIPI CSI HDR: virtual channel mode, identification code mode, line counter mode

-

Support RAW rounding

-

Support window cropping

-

Support 4/8/16/32 times down-sampling for RAW data

-

Support RAW 2×2 binning

-

Support pixel extraction from 2×2 pattern

-

Support UV mean down sampling for YUV422

-

Support reducing frame rate

-

Support compact/non-compact output format for RAW data

-

Support NV16/NV12/YUV400/YUVY output format for YUV data

-

Support virtual stride when write to DDR

-

Support DMA wrap mode

-

Support DMA burst gather 2/4/8

-

Support MMU

-

Support QOS (hurry/press)

-

Support sending RAW data directly to ISP

-

Support soft reset, auto-reset when DMA error

-

Support debug mode

-

-

Image Signal Processor V3.5

-

One channel ISP, 12M pixels

-

VICAP input: RX raw8/raw10/raw12/raw14/raw16

-

Maximum input: 4096×3072

-

Minimum input: 264×264

-

3A: include Auto Enhance (AE)/Histogram, Auto Focus (AF) and Auto White Balance (AWB) statistics output

-

FPN: Fixed Pattern Noise removal

-

BLC: Black Level Correction

-

DPCC: Static/Dynamic defect pixel cluster correction

-

PDAF: Phase Detection Auto Focus

-

LSC: Lens Shading Correction

-

Bayer-3DNR: Temporal Bayer-raw Noise Reduction

-

CAC: Chromatic Aberration Correction

-

HDR-Merge: 2-Frame Merge into High-Dynamic Range

-

Expander: Sensor Expander

-

GIC: Green Imbalance Correction

-

HDR-DRC: HDR Dynamic Range Compression, tone mapping in RGB filed

-

DeBayer: Advanced adaptive demosaic

-

CCM/CSM: Color Correction Matrix, RGB2YUV

-

Gamma: Gamma out correction

-

Dehaze/Enhance: Automatic dehaze and effect enhancement

-

LocalHist: local histogram to enhance local contrast

-

HSV: Hue, Saturation, Value color palette for customer

-

LDCH: Lens Distortion Correction in the Horizontal direction

-

LDCV: Lens Distortion Correction in the Vertical direction

-

YNR: Spatial luma (Y) Noise Reduction in YUV domain

-

CNR: Spatial chroma (C) Noise Reduction in YUV domain

-

Sharp: Image sharpening and boundary filtering

-

CGC: Color Gamut Compression, YUV full range/limit range convert

-

MI 2 paths output, MP stepless scaling, SP 1080p (width no more than 1920) scaling

-

Online mode: support data from VICAP and data to Encoder, data from ISP to VPSS, data from VICAP to 3A

-

VPSS

-

Offline DMA input:

-

Line RGB888/ARGB888/RGB565/UYVY/YUV422/420sp 8bits

-

Tile4x4 YUV422/420 8bits (Rotate 0/90/180/270)

-

RKFCBD64x4 YUV444/422/420 8bits

-

Line-Rot90 UYVY/YUV422/420sp 8bits (Rotate 90)

-

-

Online ISP input

-

Both DMA and ISP input

-

Four output channels

-

Maximum image resolution: 4096×3072 (width no more than 4096)

-

Minimum image resolution: 32×32

-

YUV422 processing

-

MIRROR: Horizontal Mirror

-

CMSC: Cover or Mosaic in 8 areas

-

CROP: Cropping on 4 channels

-

Channel0 output:

-

Scale: Polyphase filter

-

ASPT_RATIO: Aspect Ratio for image boundary extension

-

Output scan order: Line YUV422/420/400sp 8bits

-

Flip: Vertical Flip

-

-

Channel1 output:

-

Scale: Bilinear filter

-

ASPT_RATIO: Aspect Ratio for image boundary extension

-

Output scan order: Line RGB888/ARGB888/RGB565/YUV422/420sp 8bits

-

Flip: Vertical Flip for YUV mode

-

-

Channel2 output:

-

Scale: Bilinear or average filter (output width no more than 1920)

-

ASPT_RATIO: Aspect Ratio for image boundary extension

-

Output scan order: Line YUV422/420sp 8bits

-

Flip: Vertical Flip

-

-

Channel3 output:

-

Scale: Bilinear filter (output width no more than 1920)

-

ASPT_RATIO: Aspect Ratio for image boundary extension

-

Output scan order: Line YUV422/420sp 8bits

-

Flip: Vertical Flip

-

-

Sharpen: Image sharpening, input-data from the scale’s output of channel0 or channel1 or channel2

Video Output Processor

-

Video output interface

-

One PARA interface, support RGB/BT656/BT1120. Maximum resolution of PARA interface is 1920×1080@60Hz.

-

One MIPI DSI1.2 interface, up to 4lane×2.5Gbps

-

One eDP 1.3 interface, up to 4lane×5.4Gbps, with HDCP1.3

-

One HDMI 2.1 interface, up to 4lane×6Gbps, with HDCP2.3

-

-

Video Port

-

Video Port0 supports up to 4096×2160@60Hz with 10-bit data

-

Video Port1 supports up to 1920×1080@60Hz with 8-bit data

-

Each Video Port may connect to any of HDMI/eDP/DSI/PARA interface

-

-

Data format

-

Raster:

-

RGBA8888/RGB888/RGB565/RGB1010102

-

YUV444/YUV422/YUV420/YUV400, 8/10-bit

-

-

Tile 4×4

-

YUV420/YUV422/YUV444, 8/10-bit

-

-

AFBCD

-

RGBA8888/RGB888/RGBA1010102

-

YUV420/YUV422/YUV444, 8/10-bit

-

-

RFBCD

-

RGBA8888/RGB888/RGBA1010102

-

YUV420/YUV422/YUV444, 8/10-bit

-

-

-

Layer

-

Support 2 cluster layers, 2 esmart layers, 2 msmart layers, 2 cursor layers

-

FBCD data is only supported in cluster layer

-

Layer split is only supported in cluster layer

-

Multi-region is only supported in esmart layer

-

Up to 8×8 regions in 4k multi-grid layer, 6×6 regions in 2k multi-grid layer

-

Support Data swap, replication, offset, virtual display

-

Support CSC (color domain and color range convert)

-

Support Scaler up/down (ratio 8~1/8) except for multi-grid layers.

-

-

Overlay

-

Support Layer position exchange

-

Support transparency color key and 8bit alpha blending

-

Support per-pixel alpha, pre-multiplied alpha, global alpha

-

Support RGB or YUV domain overlay

-

-

Post process

-

Support Post scale Algorithm: bilinear (ratio 0.5~1)

-

Support Dither down Algorithm: 2d

-

Support CSC, color domain and color range convert.

-

Support Gamma/3D-LUT

-

Support ACM, auto color management

-

Support DCI, dynamic contrast improvement

-

Support SHARPNESS

-

Support HDR10, HDR vivid

-

-

Write Back

-

Format: ARGB8888/RGB888/RGB565/YUV420

-

Max resolution: 1920×1080

-

Support automatic write back and one frame write back model

-

Support horizontal scaled and gt2

-

Support virtual stride

-

Display interface

-

HDMI/eDP TX interface

-

One HDMI/eDP TX combo PHY

-

HDMI interface

-

HDMI v2.1

-

Supports up to 4K@60Hz

-

Output data format: RGB/YUV444/YUV422/YUV420 8/10-bit

-

Supports CEC (Consumer Electronic Control) and ARC (Audio Return Channel)

-

HDCP v2.3 and HDCP v1.4

-

-

eDP interface

-

eDP v1.3 and compliant with DisplayPort v1.2

-

Main link containing 4 physical lanes

-

Each lane supports RBR (1.62Gbps), HBR (2.7Gbps) and HBR2 (5.4Gbps)

-

Supports up to 4K@60Hz

-

Output data format: RGB/YUV444/YUV422 8/10-bit

-

Supports HDCP v1.3

-

Supports PSR (Panel Self Refresh)

-

Supports I2S (up to 8 channels) and S/PDIF audio interface

-

Supports AUX and reading of the display EDID

-

-

-

MIPI DSI-1.2 TX interface

-

One MIPI DSI V1.2 interface with D-PHY

-

Supports 4 data lanes on D-PHY with up to 2.5Gbps per lane

-

-

Parallel output interface

-

Supports RGB/BT.656/BT.1120

-

Supports up to 1920×1080@60Hz

-

Supports RGB (up to 8bit) format

-

-

EBC output interface

-

Supports E-ink EPD (Electronic Paper Display)

-

Supports up to 1872×1404 with hardware decoding

-

Supports data bus with 16-bit width

-

Supports up to 32 level gray scale

-

Supports Direct mode, LUT mode and 3-window mode

-

Supports window display mode

-

Serial Audio Interface (SAI)

-

Supports six SAI interfaces

-

SAI 0/1 support 4 TX lanes and 4 RX lanes

-

SAI 2/3 support 1 TX lane and 1 RX lane

-

SAI 4 support 4 TX lanes and 4 RX lanes, can be connected to HDPTXPHY or IO

-

SAI 5 support 4 RX lanes, it is connected to HDPTXPHY

-

-

Supports I2S/TDM/PCM mode

-

Supports 3 I2S formats (normal, left-justified, right-justified)

-

Supports master and slave work mode, software configurable

-

Supports 4 PCM formats (early, late1, late2, late3)

-

Supports TDM normal, 1/2 cycle left shift, 1 cycle left shift, 2 cycle left shift, right shift mode serial audio data transfer

-

Supports sample rate is up to 192KHz

-

Supports audio resolution is from 16bits to 32bits

-

SPDIF TX

-

SPDIF TX 0/1 are connected to IO

-

SPDIF TX 2 is connected to HDPTXPHY

-

Supports two 16-bit audio data store together in one 32-bit wide location

-

Supports bi-phase format stereo audio data output

-

Supports 16 to 31-bit audio data left or right justified in 32-bit wide sample data buffer

-

Supports 16,20,24 bits audio data transfer in linear PCM mode

-

Supports non-linear PCM transfer

-

-

SPDIF RX

-

SPDIF RX 0 is connected to IO

-

SPDIF RX 1 is connected to HDPTXPHY

-

Supports one internal 30-bit wide and 32-location deep FIFO for receiving audio data

-

Supports combined interrupt output

-

Supports DMA handshaking interface and configurable DMA water level

-

Supports liner PCM (IEC60958) and non-liner PCM (IEC61937)

-

Supports 16~24 bits audio sample length for liner PCM application

-

Supports 16 bits audio sample length for non-liner PCM application

-

SPDIF RX 0 supports up to 192kHz sample rate

-

SPDIF RX 1 supports up to 384kHz sample rate

-

Supports recovering clock and audio data from input bit-stream

-

-

PDM

-

Supports up to 8 channels

-

Supports resolution is from 16bits to 24bits

-

Supports sample rate is up to 192kHz

-

Supports PDM master receive mode

-

Supports gain control

-

-

ASRC

-

Support 2 2-channel ASRCs, which combine into 4-channel ASRC

-

Support typical THD+N -130dB

-

Support real-time transmission mode, which transmits or receives audio data from either audio component or memory with ratio tracking

-

Support memory fetch mode, which transmits or receives audio data from memory with manual ratio without tracking

-

-

Digital Audio Codec

-

Support 2 channels digital DAC

-

Support I2S/PCM interface, master and slave mode

-

Support 16-bit sample resolution

-

Support three modes of mixing for every digital DAC channel

-

Support volume control

-

Connectivity

-

SDIO interface

-

SDIO v3.0 4-bit data bus widths

-

-

GMAC 10/100/1000M Ethernet controller

-

Supports two Ethernet controllers

-

Supports IEEE 802.3 10/100/1000 Mbps Ethernet MAC with RGMII or RMII

-

Supports both full-duplex and half-duplex operation

-

-

Combo high speed interface

Others

-

Multiple group of GPIO

-

All of GPIOs can be used to generate interrupt

-

Supports level trigger and edge trigger interrupt

-

Supports configurable polarity of level trigger interrupt

-

Supports configurable rising edge, falling edge and both edge trigger interrupt

-

Supports configurable pull direction (a weak pull-up and a weak pull-down)

-

Supports configurable drive strength

-

-

Temperature Sensor (TS-ADC)

-

Supports User-Defined Mode and Automatic Mode

-

In User-Defined Mode, start_of_conversion can be controlled completely by software, and also can be generated by hardware.

-

In Automatic Mode, the temperature of alarm (high/low temperature) interrupt can be configurable

-

In Automatic Mode, the temperature of system reset can be configurable

-

Supports 5-channel TS-ADC with the temperature criteria can be configurable

-

-40~125°C temperature range and 1°C temperature resolution

-

-

Successive approximation ADC (SARADC)

-

Supports 12-bit resolution

-

Supports up to 1MS/s sampling rate

-

Supports 8 single-ended input channels

-

-

OTP

-

Supports 16-kbit space and higher 4kbit address space is non-secure part.

-

Supports read and program word mask in secure model

-

Supports maximum 32 bit OTP program operation

-

Supports maximum 16 word OTP read operation

-

Program and Read state can be read

-

Program fail address record

-

-

Package Type

-

FCCSP550L (body: 14.3mm x 15.5mm; ball size: 0.25mm; ball pitch: 0.42mm & 0.52mm & 0.65mm mixed)

-