V851S/V851SE 是一款面向 IP 摄像头领域的新型高性能 H.264/H.265 编码 SoC。它集成了单个 Cortex-A7 核心(900MHz)、RISC-V(600MHz)和 0.5 Tops NPU,支持各种智能应用,如人体检测和越界报警。V851S/V851SE 还配备了新一代高性能 ISP 图像处理器和专业编码质量、低编码码率以及主流水平的图像处理能力的视频编码器。此外,V851S/V851SE 支持 64MB DDR2 和丰富的外围接口,如 USB、SDIO 和以太网,以满足各种 IP 摄像头产品的需求。

芯片差异

V851S/V851SE 在不同设备中配置了不同的功能集。不同设备之间的功能差异如下表所示。对于详细引脚,请参阅 V851S_PINOUT和 V851SE_PINOUT文件。

表 1-1 设备功能差异

| 内容 | V851S | V851SE |

|---|---|---|

| 以太网 | 10/100 Mbit/s 以太网端口,带 RMII 接口 | SIP 100 M EPHY |

| GPIOs | 6 个端口(PA、PC、PD、PE、PF、PH) | 5 个端口(PA、PC、PE、PF、PH) |

| LCD | 平行 RGB、串行 RGB、i8080、BT656 | 不支持 |

| SPI | SPI x4(SPI0、SPI1、SPI2、SPI3) | SPI x3(SPI0、SPI2、SPI3) |

| MIPI DSI | 1 x 2-lane | 不支持 |

应用场景

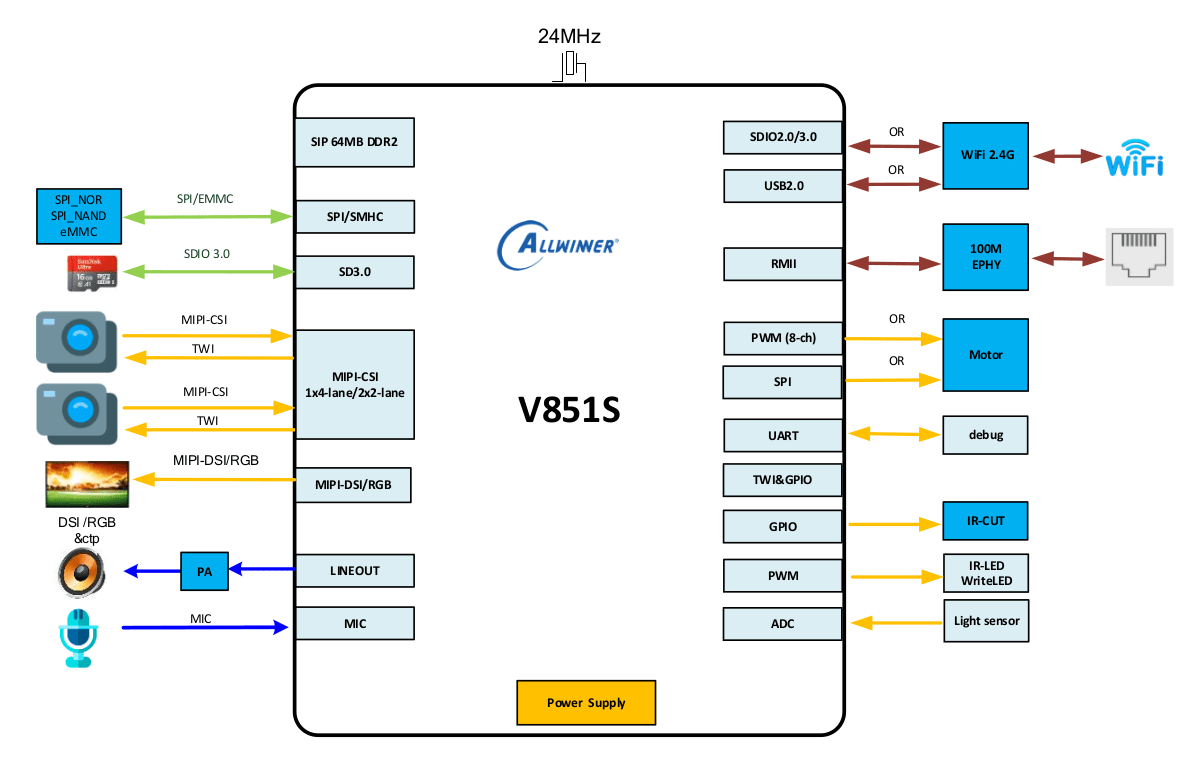

V851S

下图展示了 V851S 的应用场景。

V851S 高清 IP 摄像头解决方案

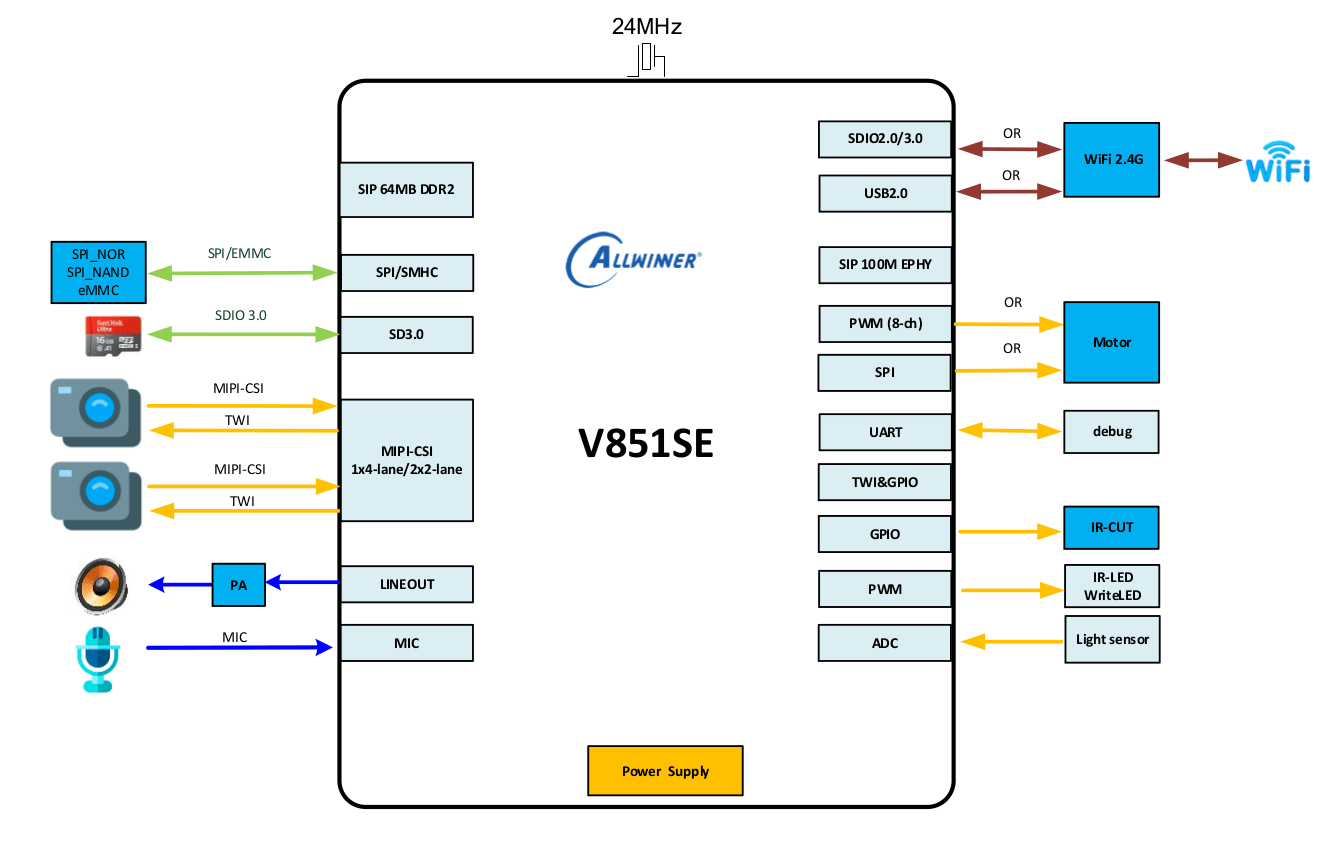

V851SE

下图展示了 V851SE 的应用场景。

V851SE 高清 IP 摄像头解决方案

SoC架构

块图

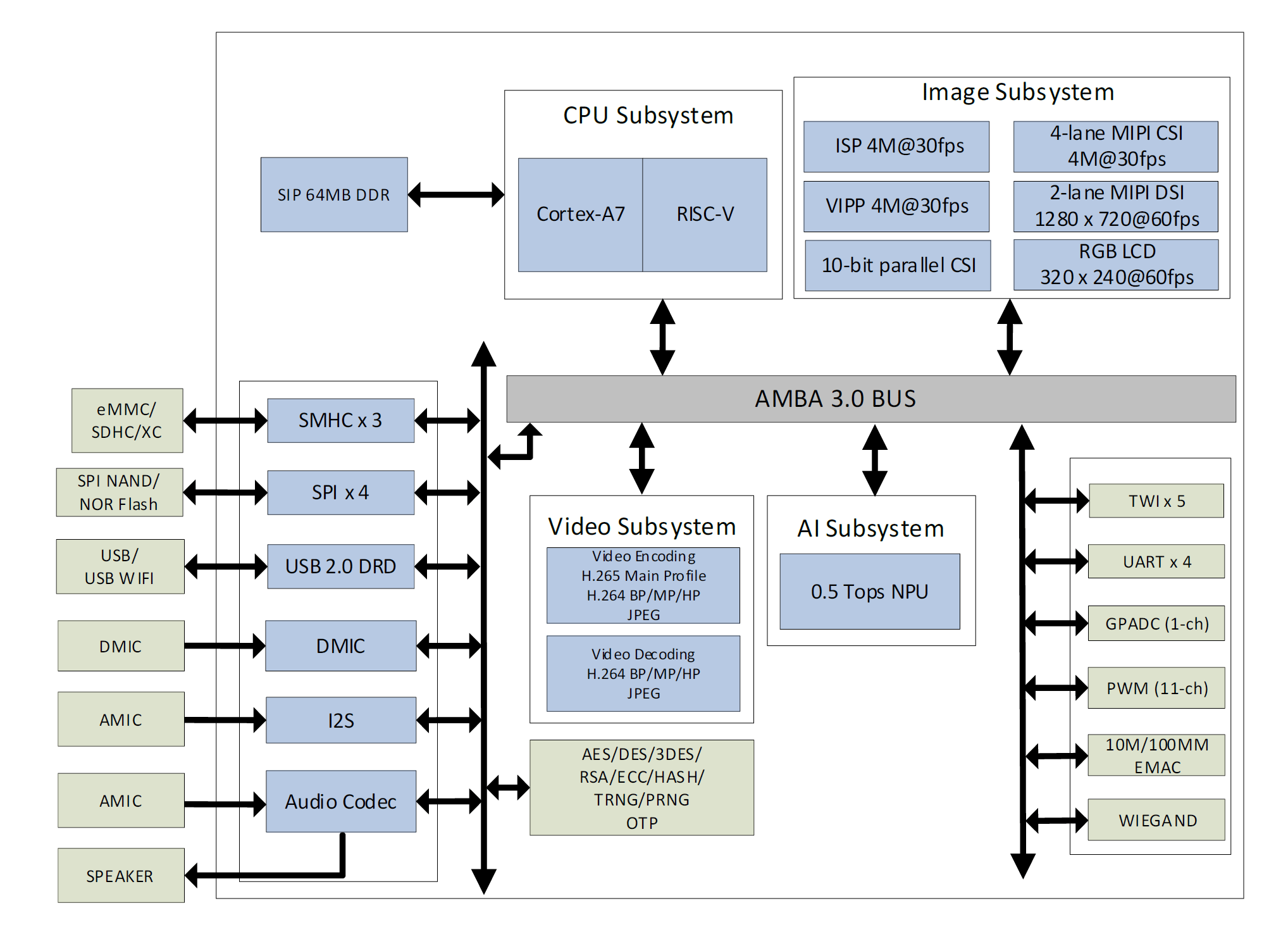

V851S

下图展示了 V851S 的逻辑块图。

V851S 逻辑块图

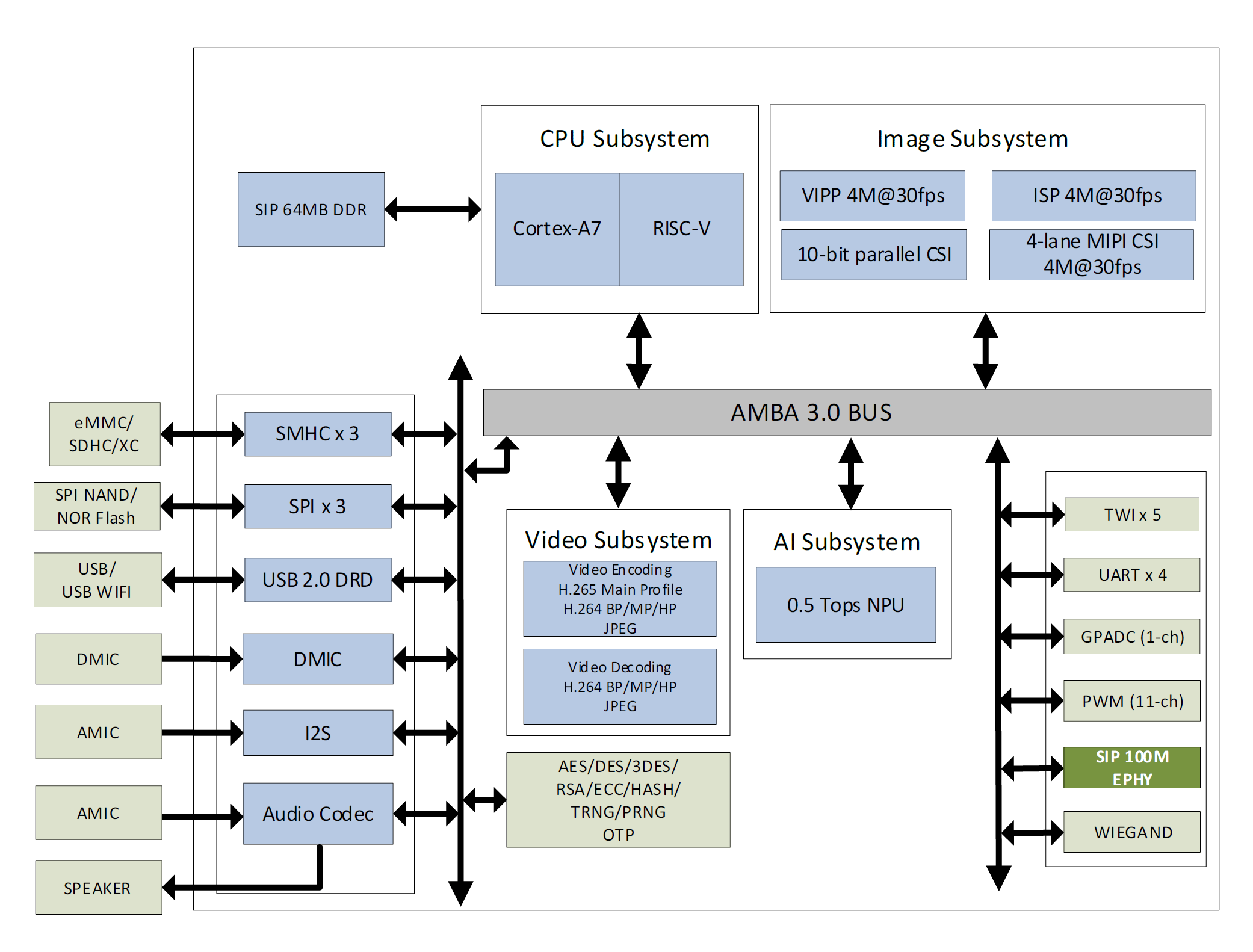

V851SE

下图展示了 V851SE 的逻辑块图。

V851SE 逻辑块图

CPU 架构

Cortex-A7 CPU 核心,支持 32 KB I-cache、32 KB D-cache 和 128 KB L2 缓存

RISC-V 核心,支持 16 KB I-cache 和 16 KB D-cache

NPU 架构

NPU最大性能可达 0.5 Tops

嵌入式 128KB 内部缓冲区

支持深度学习框架:TensorFlow、Caffe、Tflite、Pytorch、Onnx NN 等

视频编码/解码性能

H.264 BP/MP/HP 编码

H.265 MP 编码

H.264/H.265 支持 I/P 帧类型

MJPEG/JPEG 基线编码

H.264/JPEG 解码

H.264/H.265 解码的最大分辨率为 1600 万像素(4096×4096)

最多支持八个 ROI

CBR、VBR 和 FIXEDQP 模式

JPEG 编码器支持 1080p@60fps@400MHz

H.264/H.265 编码器支持 3840×2160@20fps@400MHz

H.264/H.265 多流实时编码能力:5M@25fps + 720p@25fps

视频输出

注意

V851SE 不支持 MIPI DSI 和 LCD。

MIPI DSI

符合 MIPI DSI V1.02 和 MIPI DPHY V1.2

支持 2-lane MIPI DSI,最高可达 1280×720@60fps

支持正常模式和突发模式

每通道最高可达 1.0 Gbps

TCONLCD

i8080 接口,最高可达 800 x 480@60fps

串行 RGB 接口,最高可达 800 x 480@60fps

RGB 接口,带 DE/SYNC 模式,最高可达 1920 x 1080@60fps

支持 BT656 接口

视频输入

ISP

支持 1 个独立的图像信号处理器(ISP),最大分辨率为 2560 x 1440(在线模式)

最大帧率为 4M@30fps

支持离线模式

支持 WDR 分割、2F-WDR 行基缝合、动态范围压缩(DRC)、色调映射、数字增益、伽马校正、缺陷像素校正(DPC)、串扰校正(CTC)和色差校正(CAC)

支持 2D/3D 噪声降低、拜耳插值、锐化、白平衡和色彩增强

可调 3A 功能:自动白平衡(AWB)、自动曝光(AE)和自动对焦(AF)

支持防闪烁检测统计和直方图统计

支持图形镜像和翻转

VIPP

四个 VIPP YUV422 或 YUV420 输出

最大分辨率为 2560×1440

每个 VIPP 在在线模式下有一个子-VIPP

每个 VIPP 在离线模式下最多有四个子-VIPP,用于时间分割复用

每个子-VIPP 的功能

裁剪

高度和宽度的 1 到 1/16 缩放

16 ORLs

Parallel CSI

支持 10 位宽度

支持 BT.601 和 BT.656 接口

平行接口的最大像素时钟可达 148.5MHz

支持 ITU-R BT.656,最高可达 4*720P@30fps

MIPI CSI

支持一个 4-lane MIPI CSI 输入或两个 2-lane MIPI CSI 输入

符合 MIPI-CSI2 V1.00 和 MIPI DPHY V1.00.00

每通道最高可达 1.2 Gbps

串行接口的最大视频捕获分辨率为 4M@30fps

音频子系统

音频编解码器

一个音频数字到模拟转换器(DAC)通道

支持 16 位和 20 位样本分辨率

8 kHz 到 192 kHz DAC 采样率

95 ± 2 dB SNR@A-weight,-85 ± 3 dB THD+N

一个音频模拟到数字转换器(ADC)通道

支持 16 位和 20 位样本分辨率

8 kHz 到 48 kHz ADC 采样率

95 ± 3dB SNR@A-weight,-80 ± 3dB THD+N

一个音频输入:

一个差分麦克风输入:MICIN1P/N

一个音频输出:

一个单端线路输出:LINEOUTLP

支持动态范围控制器调整 DAC 播放和 ADC 录制

一个 128×20 位 FIFO 用于 DAC 数据传输,一个 128×20 位 FIFO 用于 ADC 数据接收

可编程 FIFO 阈值

支持中断和 DMA

I2S

一个 I2S/PCM 外部接口(I2S1),用于连接外部功率放大器和 MIC ADC

符合标准 Philips Inter-IC 声音(I2S)总线规范

左对齐、右对齐、PCM 模式和时间分割复用(TDM)格式

可编程 PCM 帧宽度:1 BCLK 宽度(短帧)和 2 BCLKs 宽度(长帧)

发送和接收数据 FIFO

可编程 FIFO 阈值

128 深度 x 32 位宽度 TXFIFO 和 64 深度 x 32 位宽度 RXFIFO

支持多种功能时钟

时钟最高可达 24.576 MHz I2S/PCM 数据输出(主模式,仅当 IO PAD 和外设 I2S/PCM 满足时序参数时)

时钟最高可达 12.288 MHz I2S/PCM 数据输入(主模式)

支持 TX/RX DMA 从接口

支持多种应用场景

最高可达 16 通道(fs = 48 kHz),通道宽度可调,从 8 位到 32 位

采样率从 8 kHz 到 384 kHz(CHAN = 2)

8 位 u-law 和 8 位 A-law 压缩样本

支持主/从模式

DMIC

支持最多 8 个数字 PDM 麦克风

支持采样率从 8 kHz 到 48 kHz

外围设备

五个 TWI 接口:TWI0、TWI1、TWI2、TWI3 和 TWI4

四个 UART 接口:UART0、UART1、UART2 和 UART3

四个 SPI 接口用于 V851S:SPI0、SPI1、SPI2 和 SPI3

三个 SPI 接口用于 V851SE:SPI0、SPI2 和 SPI3

六组 GPIO 引脚用于 V851S:PA、PC、PD、PE、PF 和 PH

五组 GPIO 引脚用于 V851S:PA、PC、PE、PF 和 PH

一个通用模拟到数字转换器(GPADC)通道:GPADC0

一个 PWM 控制器(11-ch)

安全系统

加密引擎(CE)

支持对称算法进行加密和解密:AES、DES、3DES

支持 AES 的 ECB、CBC、CTS、CFB、OFB、CBC-MAC、GCM 模式

支持 AES 的 128/192/256 位密钥

支持 DES 的 ECB、CBC、CTR、CBC-MAC 模式

支持哈希算法进行防篡改:MD5、SHA、HMAC

支持 SHA 的 SHA1、SHA224、SHA256、SHA384、SHA512

支持 HMAC 的 HMAC-SHA1、HMAC-SHA256

支持 HMAC/SHA1/SHA224/SHA256/SHA384/SHA512 的多包模式

支持硬件填充

支持公钥算法:RSA、ECC

-

-

RSA 支持 512/1024/2048/3072/4096 位宽度

-

ECC 支持 160/224/256/384/521 位宽度

-

支持 160 位硬件 PRNG,种子为 15 位

支持 256 位硬件 TRNG

支持安全和非安全接口,每个世界通过自己的接口发出任务请求

支持所有配置的字节对齐地址

安全 ID(SID)

支持 2048 位 eFuse

使用 SID_SRAM 备份 eFuse 信息

将密钥烧录到 SID

在 SID 中读取密钥使用状态

将密钥加载到 CE